计数器

在上一篇中讲到了随机访问存储器(RAM),使用 RAM 的过程中,必须设置目标操作单元的地址,也就是说你要读或写一个单元,必须知道这个单元所在的地址。而地址是由多位二进制数组成的,那么该如何方便的对地址的输入进行管理呢?答案就是使用计数器。

时钟

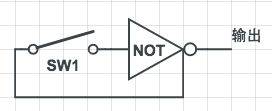

在构造一个计数器之前让我们先回忆一下振荡器:

振荡器是一个具有周期性电平输出元件,每个振荡器都有其固定频率,假设上图振荡器的频率是100Hz,那他完成一个周期性的电平输出就是0.01s,通常它的输出信号用来作为「时钟信号」,因为它的信号周期都是固定的,就好像钟表里的秒针一样。

分频器

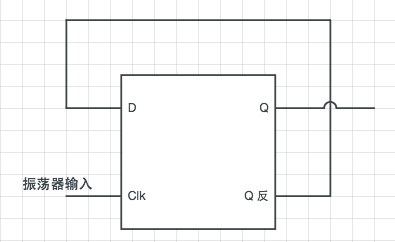

如果把振荡器的输出与边沿触发的 D 型触发器的时钟输入进行连接,同时把Q反连接到触发器的 D 输入端:

当电路启动时,时钟输入为0,Q 为0,Q反 为1,则 D 为1。

当时钟从0跳变至1瞬间,Clk 为1,因为D 此时为1,所以 Q 为1,Q反 为0。在 Clk 变为1后,由于Q反连接到了 D,所以此时 D 又变成了0。

当时钟从1变至0时,Clk 为0,Q 仍为1,Q反仍为0,D 为0。

当时钟从0又变为1的瞬间,Clk 为1,D 为0,Q 为0,Q反为1。再 Clk 变为1后,D 为1,Q 为0,Q反为1。

现在时钟的一个周期就走完了,来看一下在这个周期内的触发器输出 Q:

| 输入 | 输入 | 输出 | 输出 |

|---|---|---|---|

| D | Clk | Q | Q反 |

| 1 | 0 | 0 | 1 |

| 1 | ↑ | 1 | 0 |

| 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | ↑ | 0 | 1 |

| 1 | 1 | 0 | 1 |

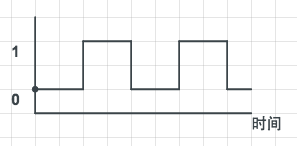

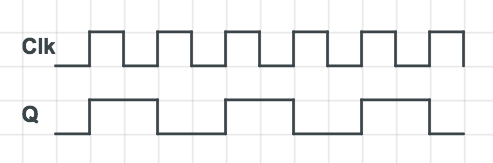

从上表可以看出,每当 Clk 从0跳变至1时,Q 就发生变化,Clk 的一个周期,相当于 Q 或者 Q反 的半个周期:

从图中可以看出,Q 的频率相对于 Clk 的频率是减半的,假设 Clk 的频率是100Hz,那 Q 的频率就是50Hz,这种电路就称为分频器。

计数器

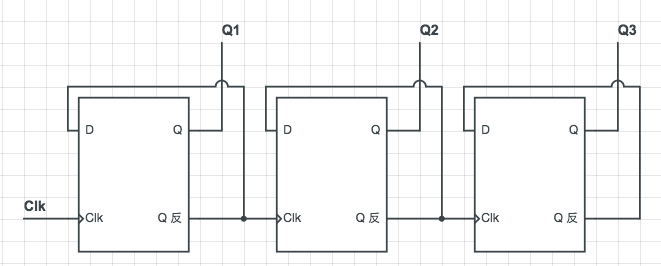

分频器的输出可以再连接一个分频器来进行再一次分频,如果将三个分频器连接:

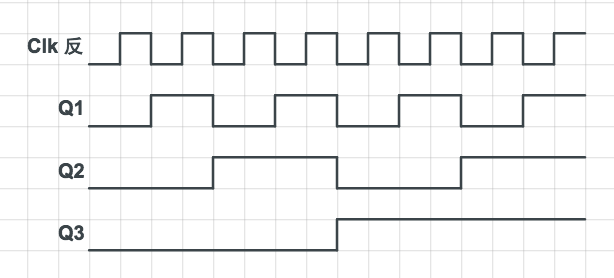

再看一下他们的 Q 输出:

因为这三个分频器的输出依次连接下一个的输入,所以下一个的输出频率是上一个的一半。如果把这张图顺时针旋转90度,你会发现这些输出之间的规律:

- 0000

- 0001

- 0010

- 0011

- 0100

- 0101

- 0110

- 0111

- 1000

- 1001

- 1010

- 1011

- 1100

- 1101

- 1110

- 1111

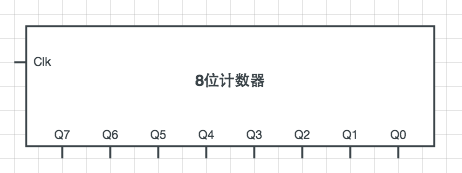

这些输出的组合,依次构成了4位连续的二进制数,而且随着时钟的不断输入,整体输出范围在0000-1111之间不断循环,这就构成了一个以时钟信号驱动的「8位计数器」,我们可以使用下面的结构表示它: